Islamic Azad University Tehran Science and Research (East Azarbaijan Branch)

# A Thesis Submitted in Partial Fulfillment of the Requirements for the Master of Science Degree in Computer Engineering – Computer System Architecture

# Subject:

Lightweight Hybrid Block-Stream Cryptographic Algorithm for the Internet of Things<sup>1</sup>

# Thesis SEPARvisor:

Mir Kamal Mirnia Herikandi (Ph. D.)

Thesis Advisor:

# **By:** Arsalan Vahi

Spring 2020 Technical and Engineering Department

<sup>&</sup>lt;sup>1</sup> This document has been translated from a Persian thesis.

The contents of this thesis are based on the article "SEPAR: A New Lightweight Hybrid Encryption Algorithm with a Novel Design Approach for IoT, which was previously published in "Wireless Personal communication" Journal. The article represents a part of the research work conducted for this thesis.

#### Abstract

In this thesis, a novel lightweight hybrid encryption algorithm named **SEPAR** is proposed, featuring a 16-bit block length and a 128-bit initialization vector. The algorithm is designed specifically for application in Internet of Things (IoT) technology devices. The design concept of this algorithm is based on the integration of a pseudo-random permutation function and a pseudo-random generator function. This intelligent combination not only enhances the algorithm's resistance against cryptographic attacks but also improves its processing speed. The security analyses conducted on the algorithm, along with the results of NIST statistical tests, confirm its robustness against most common and advanced cryptographic attacks, including linear and differential attacks. The proposed algorithm has been implemented on various software platform architectures. The software implementation was carried out on three platforms: 8-bit, 16-bit, and 32-bit architectures. A comparative analysis with the **BORON** algorithm on a 32-bit ARM processor indicates a performance improvement of **42.25%**. Furthermore, implementation results on 8-bit and 16-bit microcontrollers demonstrate performance improvements of **87.91%** and **98.01%** respectively, compared to the **PRESENT** cipher.

**Keywords:** Lightweight cryptographt-Internet of things- cryptographic attacks-Software Implementation

# **Table of Contents**

# **Chapter 1: Introduction to the Internet of Things and Study**

# Background

| Introduction                                      | 2 |

|---------------------------------------------------|---|

| 1.1 Introduction to the Internet of Things        | 2 |

| 1.3 Security Challenges on the Internet of Things | 5 |

| 1.4 Study Background                              | 7 |

| 1.5 Thesis Structure                              | 7 |

| Summary and Conclusion                            | 8 |

# **Chapter 2: Literature Review on Lightweight Encryption Algorithm**

# Design

| Introduction                                                         | 10 |

|----------------------------------------------------------------------|----|

| 2.1 Cryptography                                                     | 10 |

| 2.2 Lightweight Cryptography                                         | 11 |

| 2.3 Symmetric and Asymmetric Cryptosystems and Their Characteristics | 12 |

| 2.3.1 Comparatison of Symmetric and Asymmetric Encryptions           | 14 |

| 2.4 Block and Stream Cipher Techniques: Features and Evaluation      | 15 |

| 2.4.1 Block Ciphers                                                  | 15 |

| 2.4.1.1 Core Components Used in a Block Cipher                       | 15 |

| 2.4.2 Stream Ciphers                                                 | 18 |

| 2.4.3 Comparison                                                     | 20 |

| 2.5 Existing Lightweight Symmetric Encryption Algorithms             | 22 |

| 2.5.1 PRESENT Cipher                                                 | 22 |

| 2.5.2 BORON Cipher                                                   | 23 |

| 2.5.3 Hummingbird Cipher                                             | 24 |

| 2.5.4 Comparison                                                 | 25 |

|------------------------------------------------------------------|----|

| Summary and Conclusion                                           | 25 |

| Chapter 3: Design and Implementation of the Proposed Algorithm   |    |

| Introduction                                                     | 24 |

| 3.1 Design Strategy                                              | 24 |

| 3.2 SEPAR Encryption System                                      | 25 |

| 3.2.1 Initialization Process                                     | 26 |

| 3.2.2 Encryption Process                                         | 28 |

| 3.2.3 Decryption Process                                         | 30 |

| 3.2.4 Key Generation Algorithm                                   | 32 |

| 3.2.5 16-bit Block Cipher                                        | 33 |

| 3.2.5.1 Criteria for choosing S-Boxes                            | 34 |

| 3.2.6 Criteria for choosing LFSR                                 | 37 |

| 3.2.6 Design Logic of the SEPAR Cipher                           | 45 |

| 3.2.7 Security Analysis                                          | 45 |

| 3.2.8 Implementation                                             | 55 |

| 3.2.9 Software Implementation on an 8-bit Microcontroller        | 57 |

| 3.2.10 Software Implementation on a 32-bit Microprocessor        | 60 |

| 3.2.11 Software Implementation on a 16-bit Microcontroller       | 64 |

| 3.2.12 Other Software Implementations                            | 68 |

| Summary and Conclusion                                           | 68 |

| Chapter 4: Conclusion and Future Work                            |    |

| 4.1 Introduction                                                 | 70 |

| 4.2 Performance Improvement Evaluation on 8-bit Microcontroller  | 70 |

| 4.3 Performance Improvement Evaluation on 16-bit Microcontroller | 71 |

| References                                                       | 75 |

|------------------------------------------------------------------|----|

| 4.5 Future Work                                                  | 74 |

| 4.4 Performance Improvement Evaluation on 32-bit Microcontroller | 73 |

| 4.3 Performance Improvement Evaluation on 16-bit Microcontroller | 71 |

# List of Figures

| Figure 1.1: IoT System Architecture                                          | 3  |

|------------------------------------------------------------------------------|----|

| Figure 1.2: Operation of a Symmetric Cryptographic System                    | 12 |

| Figure 2.1: Operation of an Asymmetric Cryptographic System                  | 13 |

| Figure 2.2: General Structure of a Block Cipher Algorithm                    | 16 |

| Figure 2.3:SPN and Feistel Structures                                        | 18 |

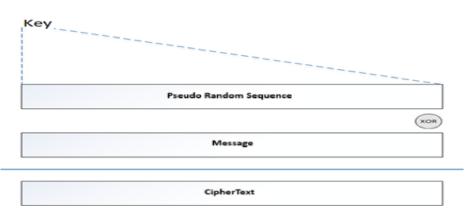

| Figure 2.4: Structure of Stream Cipher Algorithms                            | 19 |

| Figure 2.5: SchematicRepresentation of the PRESENT Cipher                    | 23 |

| Figure 2.6: SchematicRepresentation of the BORON Cipher                      | 24 |

| Figure 2.7: Schematic Representation of the Hummingbird Cipher               | 25 |

| Figure 3.1: Design Trade-Offs for Developing a Lightweight Cryptographic     |    |

| Algorithm                                                                    | 28 |

| Figure 3.2:SEPAR Preprocessing Algorithm                                     | 30 |

| Figure 3.3:SEPAR Encryption Algorithm                                        | 32 |

| Figure 3.4:SEPAR Decryption Algorithm                                        | 34 |

| Figure 3.5:16-bit Block Cipher                                               | 37 |

| Figure 3.6:ENC-BLOCK Structure                                               | 38 |

| Figure 3.7: Differential Distribution Table of the S-box                     | 43 |

| Figure 3.8: Linear Approximation Table of the S-box                          | 43 |

| Figure 3.9:800 Output Samples from the Linear Feedback Register              | 44 |

| Figure 3.10: Differential Characteristics Path                               | 48 |

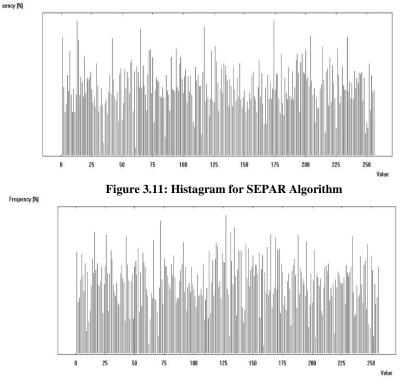

| Figure 3.11: Histogram for the SEPAR Algorithm                               | 53 |

| Figure 3.12: Histogram for the AES Algorithm                                 | 53 |

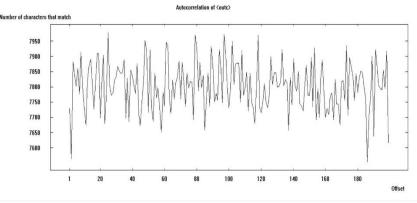

| Figure 3.13: Autocorrelation Diagram                                         | 54 |

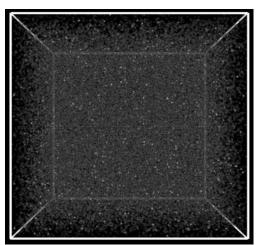

| Figure 3.14:3D Representation of Cipher Output                               | 55 |

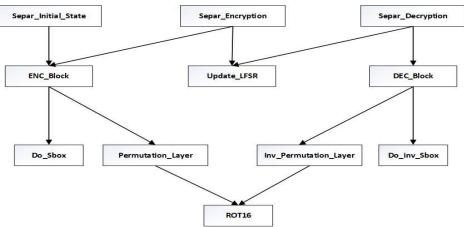

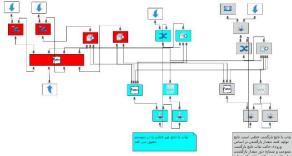

| Figure 3.15: Function Call Graph Used in the Implementation                  | 57 |

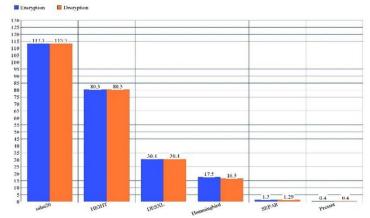

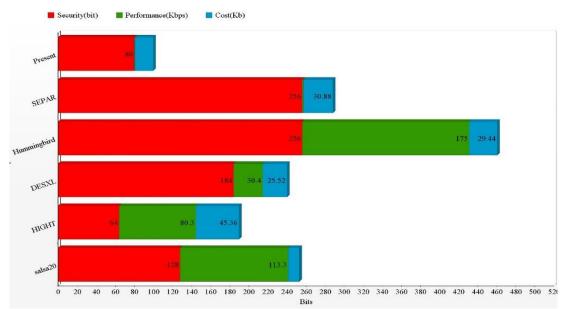

| Figure 3.16:Performance Comparison of Encryption Algorithms on 8-bit         |    |

| Microcontroller                                                              | 59 |

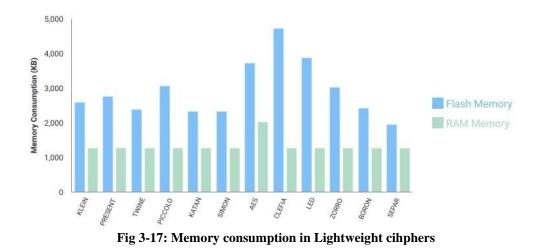

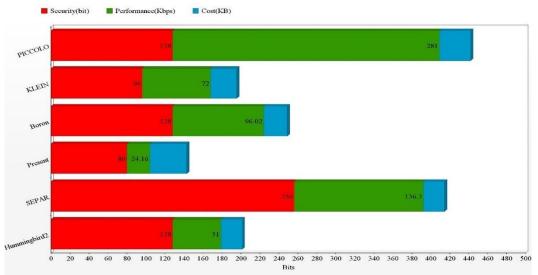

| Figure 3.17: Memory Usage in Lightweight Algorithms                          | 63 |

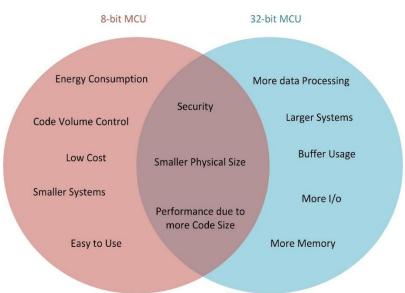

| Figure 3.18: Venn Diagram of Parameters in 8-bit and 32-bit Microcontrollers | 64 |

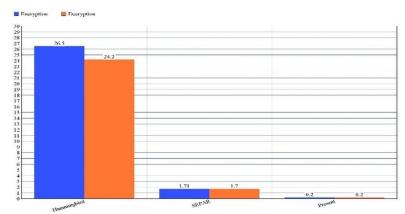

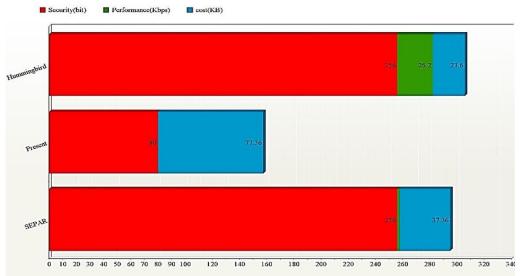

| Figure 3.19:Performance Comparison of Encryption Algorithms on 16-bit        |    |

| Microcontroller                                                              | 67 |

| Figure 3.20:Implementation of SEPAR Algorithm in the TARA Framework          | 68 |

| Figure 4.1: Design Objective Comparison (Security, Cost, and Per  | formance) in 8-bit  |

|-------------------------------------------------------------------|---------------------|

| Microcontroller                                                   | 71                  |

| Figure 4.2: Design Objective Comparison (Security, Cost, and Perf | formance) in 16-bit |

| Microcontroller                                                   | 72                  |

| Figure 4.3: Design Objective Comparison (Security, Cost, and Perf | formance) in 32-bit |

| Microcontroller                                                   | 73                  |

# List of Pseudocodes

| Pseudocode 3.1:SEPAR Preprocessing Algorithm | - 31 |

|----------------------------------------------|------|

| Pseudocode 3.2 :SEPAR Encryption Algorithm   | -33  |

| Pseudocode 3.3:SEPAR Decryption Algorithm    | 35   |

| Pseudocode 3.4: Subkey Generation Algorithm  | -36  |

| Pseudocode 3.5: ENC-BLOCK Operation Process  | .39  |

# List of Tables

| Table 1.1: Overview of Proposed Solutions with Layered IoT Architecture         | 7   |

|---------------------------------------------------------------------------------|-----|

| Table 2.1: Comparison of Features between Symmetric and Asymmetric Cryptograph  | hic |

| Systems                                                                         | -14 |

| Table 2.2: Comparison of Block and Stream Cipher Methods                        | ·21 |

| Table 2.3: Comparative Analysis of Common Lightweight Ciphers                   | 25  |

| Table 3.1:Notation Used                                                         | 29  |

| Table 3.2:Hexadecimal Representation of the S-box                               | -37 |

| Table 3.3: Differential Characteristics for the BI16 Function                   | 46  |

| Table 3.4:Number of Differential Characteristics with High Probability          | -47 |

| Table 3.5:Comparison of Number of S-boxes, Polynomial Equations, and Variables  | -49 |

| Table 3.6: Analysis of Avalanche Effect                                         | -50 |

| Table 3.7:NIST Statistical Tests Evaluation                                     | ·52 |

| Table 3.8:Entropy Comparison of SEPAR with Well-known Algorithms                | 54  |

| Table 3.9 :IoT Development Boards and Tools with Common Microcontrollers and    |     |

| Microprocessors                                                                 | -56 |

| Table 3.10:Key Features of 8-bit ATmega128L Microcontroller                     | -57 |

| Table 3.11:Comparison of Machine Cycles (Optimized Memory Implementation on 8   | 8-  |

| bit MCU)5                                                                       | 58  |

| Table 3.12:SEPAR Encryption Time for Three Different Data Lengths at 4 MHz      | 60  |

| Table 3.13:SEPAR Encryption Time for Three Different Data Lengths at 4 MHz      | 60  |

| Table 3.14:Key Features of LPC2129 Microcontroller with ARM7 Core               | -61 |

| Table 3.15:Number of Machine Cycles on 32-bit MCU at 12 MHz                     | 62  |

| Table 3.16:SEPAR Execution Time for 64, 128, and 192-bit Data at 12 MHz         | -63 |

| Table 3.17:Efficiency and Encryption Time of Common Lightweight Algorithms      | -63 |

| Table 3.18 :Key Features of MSP430F1611 Microcontroller                         | -65 |

| Table 3.19 :Memory Usage and Machine Cycles (Optimized Memory Implementation)   | n   |

| on 16-bit MCU)                                                                  | 66  |

| Table 3.20:Overall Encryption Performance at 4 MHz (Optimized Implementation or | 1   |

| 16-bit MCU)                                                                     | 67  |

| Table 3.21:Overall Decryption Performance at 4 MHz (Optimized Implementation or | n   |

| 16-bit MCU)6                                                                    | 57  |

| Table 4.1: Encryption Performance Improvement at 4 MHz on 8-bit MCU7            | 70  |

| <b>Table 4.2</b> :Decryption Performance Improvement at 4 MHz on 8-bit MCU70 |

|------------------------------------------------------------------------------|

| Table 4.3:SEPAR Encryption Performance Improvement at 4 MHz on 16-bit MCU71  |

| Table 4.4:SEPAR Decryption Performance Improvement at 4 MHz on 16-bit MCU72  |

| Table 4.5:SEPAR Algorithm Encryption Performance Improvement at 12 MHz on    |

| ARM 32-bit Processor73                                                       |

# Chapter 1: Introduction to the Internet of Things and Research Background

# **Objectives of the Chapter:**

- 1. Introduction to the Internet of Things (IoT)

- 2. Challenges in Securing IoT

- 3. Research Background

- 4. Thesis Structure

# Introduction

In this chapter, the concept of the Internet of Things (IoT) and the relevant research context is introduced. Initially, it provides a definition of IoT technology, followed by a discussion of its major challenges. The chapter concludes by outlining the structure of the thesis.

### **1.1 Introduction to the Internet of Things**

Advancements in embedded system manufacturing and the growing tendency toward their widespread applications, alongside the development of internet communication infrastructure—particularly driven by the popularity of wireless communication technologies over the past decade—have enabled the vision of a more convenient life through the integration and smartening of everyday objects. This concept, first proposed by Kevin Ashton in 1999, gave birth to the concept of "Internet of Things" technology [1]. IoT has emerged from the convergence of five mature technologies: ubiquitous computing, sensor networks, big data, cloud computing, and radio frequency identification (RFID) technology [2]. Key security challenges in IoT include privacy protection, scalability, and the heterogeneous structure of its networks [3]. The main goal of IoT is to integrate objects into human daily life, allowing them to participate in routine activities. However, such integration inevitably exposes personal and confidential data to surrounding smart objects. Without adequate security considerations, applying IoT to everyday objects is not practically feasible and may lead to harmful consequences rather than comfort and convenience.

IoT refers to a collection of objects within an environment that are interconnected through a dynamic public network, capable of self-configuration and communication based on standard and universally accepted protocols. These objects collect data from the environment, transmit it via the internet to a data analysis center, and receive specialized intelligent services in return [4]. Figure 1-1 presents the fundamental structure of the system. Objects within the environment—such as household items, factory equipment, street infrastructure, clothing, shoes, and balls—that need to be internet-connected, are linked to intermediary units (electronic boards and RFID tags), which translate internet-based instructions and messages into forms understandable by

the objects. Each intermediary unit connects to both an object and either the internet or a local network. Depending on their internal architecture, these units may feature Wi-Fi, USB, or other interfaces, allowing them to connect to access points and obtain unique IP addresses. This connectivity facilitates cooperation and interaction among smart objects. These units may also include internal web servers or connect to external professional web servers via the internet. Alternatively, the systems may be managed through a centralized control center on the internet, delivering services such as smart homes, smart transportation, and more, based on preconfigured plans [5].

Figure 1-1: IoT System Structure

The core and inherent characteristics of IoT systems are primarily based on ubiquitous computing and embedded systems. Typically, IoT systems exhibit the following features [6]:

• Presence of Smart Objects: Intelligence in objects arises from the integration of algorithms and computation (software and hardware). These objects must be capable of performing basic processing tasks to determine whether the environmental data they collect is significant enough to be sent to the cloud for service provision, and to make appropriate decisions.

• Object Connectivity: In a dynamic, scalable network of heterogeneous mobile objects, each object must be capable of communication and compatibility with others. Machine-to-machine (M2M) communication protocols are used to facilitate their interoperability within the network, enabling both data production and consumption.

• Energy Constraints: Most objects have limited resources and energy. They are typically equipped with low-cost, low-performance processors and possess minimal storage capacity. Moreover, many of these objects rely on batteries as their energy source, limiting the feasibility of employing complex algorithms.

• Limited Security: Due to the dynamic network structure and mobility of objects, they may enter uncontrolled environments lacking oversight, increasing their vulnerability to various threats. Sensors are often installed in publicly accessible locations, making them physically susceptible to theft and damage. Securing the objects, network, and data flow is essential for ensuring overall system security.

IoT aims to connect all potentially connectable elements capable of interacting via the Internet, thereby enabling a more secure and convenient lifestyle. Some common IoT applications include [2]:

• Energy and Power Management: Systems connected to the internet that use sensors to monitor and reduce energy consumption. Examples include smart lamps and controlled ovens.

• Home and Building Automation: IoT can function as a remote controller and monitor for household systems. Examples include phones, televisions, and similar appliances.

• **Transportation Systems**: In urban environments, IoT enables automated systems such as adjustable traffic lights and smart surveillance cameras that report less congested routes and help reroute traffic efficiently.

Given the intrinsic features of IoT outlined above, it is necessary to first study the types of potential attacks in this environment to propose an effective security solution. This is addressed in the following section.

#### **1.2 Security Challenges on the Intenet of Things**

The previous section provided an overview of the IoT concept and its applications. This section highlights common types of attacks that are crucial for security engineers to analyze. The following are notable examples:

• Authentication Attacks: A prevalent authentication method in IoT involves attaching tags containing identity information to objects, which are then read using a tag

reader. If an attacker gains access to these tags and their information, they can read or modify the data, or even duplicate and transfer it to another tag, thereby creating a forged identity [7].

• **Eavesdropping**: One of the simplest and most dangerous passive attacks, eavesdropping targets user privacy. Due to the wireless nature of communication among objects, an attacker can intercept the communication channel to listen in on transmitted information. This becomes especially serious if sensitive data such as passwords or personal details are exchanged without encryption [6].

• **Spoofing**: If an attacker injects false data into the system and the system mistakenly accepts it as originating from a legitimate source, the attacker can exploit this vulnerability to gain access.

• **Resource Drain Attacks**: In this type of attack [8], a malicious object attempts to exhaust the battery power of other objects by forcing them to perform unnecessary operations.

• Denial-of-Service (DoS) Attacks: This attack involves the attacker sending abnormal traffic to a target object, thereby preventing legitimate network traffic from reaching that object.

Based on the characteristics and attack types described above, two primary categories of security requirements in the IoT context can be defined [9]:

1. **Network Security**: Essential services in this domain include authentication, confidentiality, data integrity, and availability.

2. **Privacy and Identity**: This is one of the most challenging aspects due to the presence of individuals and the vast amount of data collected by the IoT system. The multitude of connected objects and the complex relationships among devices, services, owners, and users make privacy and identity protection particularly critical. Object owners generally do not wish to be tracked merely due to the presence of smart devices in their environments.

Meeting these security needs requires the development of appropriate security solutions, among which cryptographic techniques are considered a promising approach.

#### **1.3 Study Background**

The development of an effective cryptographic algorithm can serve as a robust security solution to provide essential security services within IoT. Table 1-1 presents a summary of proposed security solutions along with the layered architecture of the Internet of Things [10].

| IoT Layered Architecture | <u>Elements</u>                     | <u>Solutions</u>          |

|--------------------------|-------------------------------------|---------------------------|

|                          | Personlized Information Services    | Identity agreement        |

| Application Layer        | Smart Transportation Services       | Key Agreement             |

|                          | Monitoring System services          | Protecting Privacy        |

|                          |                                     | Encryption Mechanism      |

| Data Processing Layer    | Cloud Processing                    | Introsion Detection       |

|                          | Intelligence Processing             | Secure Cloud Processing   |

|                          |                                     | Antivirus and Firewalls   |

|                          | Mobile Internet Communation Netwrok | Encryption Mechanism      |

| Network Layer            | Satelite Networks                   |                           |

|                          | Communication Protocols             | Securing Commnication     |

|                          | Radio Frequency Tag Readers         | Simple Encryption         |

| Perception Layer         | Sensors                             | Key Agreement             |

|                          |                                     | Protecting Sensitive Data |

Table 1-1: Overview of Proposed Security Solutions Aligned with IoT Layered Architecture

The objective is to develop a cryptographic algorithm that meets the necessary security requirements on the Internet of Things and is designed to be multipurpose, aligning with the characteristics of IoT devices as previously discussed. In Chapter 2, lightweight cryptographic algorithms will be briefly introduced.

## **1.4 Thesis Structure**

This thesis is organized into four chapters. Chapter 1 provided a general definition of the Internet of Things and presented its key security challenges. Chapter 2 offers a comparative analysis of block and stream cipher methods, highlighting their respective features, along with a review of commonly used symmetric and public-key encryption algorithms. Chapter 3 introduces a novel cryptographic algorithm that combines concepts from both block and stream ciphering techniques. Finally, Chapter 4 presents conclusions and outlines future research directions.

# **Summary and Conclusion**

This chapter introduced the concept of the Internet of Things and the associated security challenges. Among these challenges, the development of a new lightweight cryptographic algorithm was identified as the focus of this research, and its significance was discussed. Therefore, to provide a deeper understanding, the next chapter will compare block and stream ciphering methods and explore the various features employed in existing conventional algorithms.

# Chapter 2: Literature Review on Lightweight Encryption Algorithm Design

# **Chapter Objectives:**

- Survey of Design Methodology for Lightweight Ciphers

- Analysis of Key Features in Various Cryptographic Methods

- Comparative Study of Existing Design Methods

- Proposal of a Novel Cryptographic Algorithm

# Introduction

This chapter begins with a definition of cryptography and an examination of symmetric and asymmetric cryptosystems. Given the compatibility of the Internet of Things (IoT) environment with symmetric cryptosystems, the two primary encryption methods of block cipher and stream cipher, are explored. A comparison of the advantages and disadvantages, along with an analysis of the features of these two methods, leads us to explore a balance between them and investigate previously designed lightweight cryptographic algorithms, ultimately guiding us toward the design of our own hybrid algorithm called **SEPAR**.

### 2.1 Cryptography

The term cryptography is derived from two Greek words: "crypto," meaning hidden, and "graph," meaning writing, and refers to the science of hidden information. One of the famous historical ciphers is the Caesar cipher, which was used by Julius Caesar to prevent the leakage of military information by shifting each letter by three units, thus preventing his messages from being realized by enemies. Since 1949, with the historical review by Claude Shannon, a new window was opened to modern cryptography, and competition for utilizing cryptographic capabilities in various fields, including telecommunications and information technology, began [11]. Four essential requirements for protecting systems and data against adversaries are outlined as follows [12]:

- **Confidentiality Requirement**: Only the sender and receiver of the communication should be able to understand the contents of the transmitted data. This requirement is achievable only through cryptographic solutions.

- Data Integrity Requirement: Ensures that data received in the receiving part is original and has not been altered in any way, maintaining exactly what was sent by the original sender. If the content of the communication has been modified, it must be understandable by the parties involved.

- Authentication Requirement: The sender and receiver must be able to verify each other's identities. Any fraudulent actor must be identifiable and understandable.

- Non-repudiation Requirement: Ensures that no entity can deny having performed an action previously. For instance, in network communications, the sender of a message should not be able to deny sending it.

Among these four services, **confidentiality** is the core service, and all cryptographic algorithms must provide it, whereas the provision of other services is optional.

# 2.2 Lightweight Cryptography

The 1970s marked the emergence of cryptography in both scientific and commercial spaces, with its widespread application in everyday operations. Alongside these advancements, the push for creating smaller electrical and telecommunications components with lower energy consumption gave rise to a new branch in cryptography known as **lightweight cryptography**. The main challenge in designing lightweight ciphers is striking a balance between three important parameters: security, cost, and efficiency. The security of a cryptographic algorithm depends on its throughput. To determine the cost, factors such as space, memory consumption, and code size are examined. It is important to note that in defining lightweight cryptography, no specific boundaries are set for each of these three parameters—cost, security, and efficiency— as they largely depend on the environment in which the system is deployed.

### 2.3 Symmetric and Asymmetric Cryptosystems and Their

#### Characteristics

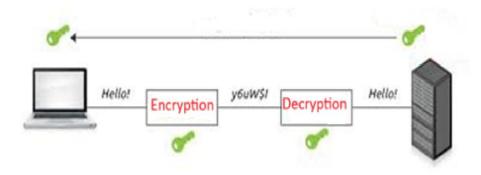

Cryptosystems are categorized into symmetric and asymmetric systems based on the number of keys used for encryption operations. Symmetric systems, also known as **secret key cryptography**, use a single shared key for both encryption and decryption. Figure 2.1 illustrates the working mechanism of this cryptosystem.

Fig 2.1: Symmetric Encryption

A fundamental requirement in the application of these cryptosystems is the ability to maintain the secrecy of the key during its exchange between the sender and the receiver. Additionally, when using these cryptosystems, employing a strong cryptographic algorithm is critical. By strong, it is meant that an adversary, having access to the encryption algorithm and the ciphertext, should not be able to reverse the operation (i.e., decrypt the message) and retrieve the key and original message.

One of the challenges with symmetric encryption algorithms is the challenge of key distribution between authorized parties, maintaining the confidentiality of the key, and the inability to provide authentication and integrity services independently or without combining with other algorithms. In contrast to these practical weaknesses, efficient hardware and software implementations of these cryptosystems have made them a viable option for applications. Symmetric encryption algorithms are classified into two categories: block ciphers and stream ciphers. By combining these two methods, a new category, known as the **hybrid category**, can also be introduced.

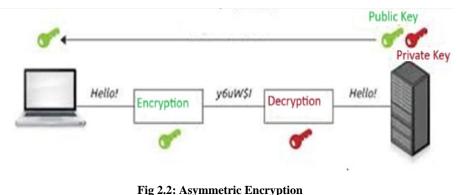

In the second category, asymmetric cryptosystems are placed. The concept of encryption in these systems is based on the idea that the algorithm does not decrypt what it encrypts with the same key; decryption is performed with a different key. Figure 2.2 shows the operation of this cryptosystem.

11

One of the two distinct keys in this cryptography is the **public key**, which is accessible to everyone, and the other is the **private key**, which is kept confidential by the user. In this method, anyone can encrypt a message with a public key, while decrypting the encrypted message is only possible with the private key associated with that public key. Although theoretically it is possible to obtain the private key from the public key, in practice, obtaining and computing requires considerable time and computational resources. Asymmetric key algorithms are significantly more secure compared to symmetric key algorithms; however, their implementation is much more complex, resulting in a much slower execution speed.

#### **2.3.1** Comparison of Symmetric and Asymmetric Encyptions

Each of the symmetric and asymmetric cryptosystems, depending on their characteristics, has its own advantages and disadvantages. Table 2.1 summarizes the advantages and disadvantages of these systems.

| Table 2.1: Comparison of Symmetric and Asymmetric Cryptosystem |                                                        |                                                                                                                                                                                                                                                                                                                                                                                          |  |

|----------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>Feature</b>                                                 | Symmetric Encryption                                   | Asymmetric Encryption                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                |                                                        |                                                                                                                                                                                                                                                                                                                                                                                          |  |

| What must                                                      | Secret: key                                            | Secret: private key                                                                                                                                                                                                                                                                                                                                                                      |  |

| remain secret and                                              | Public: plaintext and algorithm                        | Public: plaintext and algorithm                                                                                                                                                                                                                                                                                                                                                          |  |

| what is public                                                 | 1 0                                                    |                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Key length                                                     | Typically short                                        | Typically long                                                                                                                                                                                                                                                                                                                                                                           |  |

| Changing keys in communication                                 | Both parties must agree and change the key             | e Each person keeps their private key; public key is freely distributable                                                                                                                                                                                                                                                                                                                |  |

| Key Storage                                                    | Must be Securly Stored                                 | Private key must be securely stored                                                                                                                                                                                                                                                                                                                                                      |  |

| Ciphertext<br>Calculation                                      | Using two basic principles:<br>confusion and diffusion | Using complex mathematical calculations                                                                                                                                                                                                                                                                                                                                                  |  |

| Implementation<br>and design<br>aspects                        | Easier to implement                                    | Due to complex mathematical operations,<br>asymmetric encryption typically demands<br>significant computational resources. For<br>example, if implemented on an 8-bit micro with<br>limited resources, their performance is 100 or<br>1000 times slower than symmetric algorithms.                                                                                                       |  |

| Execution Speed                                                | Relatively 1000 times faster.                          | Complex mathematical calculations make them slower.                                                                                                                                                                                                                                                                                                                                      |  |

| Important<br>Applications                                      | Very Efficient for Encryption                          | Due to the high amount of cryptographic<br>calculations, these schemes are not mainly used<br>for cryptographic operations but rather are<br>mostly used in applications such as email that<br>require authentication and digital signatures.<br>They are also mostly used to establish an<br>exchange key for symmetric cryptographic<br>algorithms between communicating parties [13]. |  |

Table 2.1: Comparison of Symmetric and Asymmetric Cryptosystem

Based on the comparison in Table 2.1, it can be concluded that symmetric encryption is more suitable for resource-limited devices in the IoT environment. The

next section will examine block and stream encryption methods and study their features.

### 2.4 Bock and stream Cipher Techniques: Features and Evaluations

Since symmetric cryptosystems are suitable for resource-limited environments, the structure of algorithms used in these cryptosystems will be reviewed next. These algorithms are classified into two broad categories: block ciphers and stream ciphers.

### 2.4.1 Block Ciphers

Block ciphers begin the encryption operation by processing blocks of data. The basic function of these algorithms is based on a pseudo-random permutation, where the internal structure of the algorithm, along with the key, determines which input block is mapped to which output block.

#### 2.4.1.1 Core Components Used in Block Algorithms

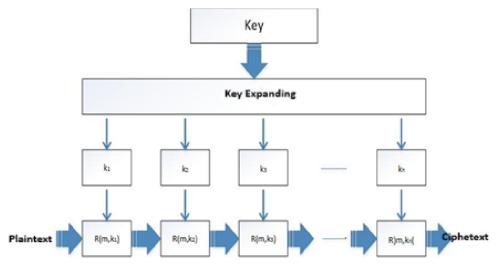

A block cipher algorithm is composed of four basic elements: key expansion, key mixing, internal structure, and round function [14]. The general structure of a block cipher algorithm is shown in Figure 2.3.

Fig2.3: Overall Schematic for a block cipher algorithm

The **key expansion element** is responsible for dividing the key input by the user into several equal-sized subkeys within the algorithm. Its structure is designed as a good pseudo-random generator, although its complexity should be much lower compared to the algorithm itself. This part can be viewed as a small algorithm that does not need to be reversible. By using a suitable generator, the analysis of subkey generation becomes difficult [14].

Block cipher round functions are divided into two categories: **confusion functions** and **diffusion functions**. Diffusion functions are linear functions that prevent leakage of any statistical information from the plaintext into the ciphertext. These functions, using linear operators, uniformly distribute the input across the output space. This property causes the influence of each bit of the plaintext or key to be spread out and minimized in the ciphertext. The goal of these functions is to create a lack of correlation between the bits of the input text, key, and output text, so that statistical relationships are eliminated, and cryptanalysis becomes more complex. One of the most commonly used elements in algorithm design to implement this feature is the **permutation box**. This element only serves the purpose of swapping the input bits, thereby achieving the diffusion property. It is a reversible function, so it can be used again to reverse the message to its previous form. This element is highly suitable for hardware implementation, as it requires no gates and is made solely of wiring. In contrast, the complexity of its software implementation arises from the need for heavy bitwise operations.

**Confusion functions** are non-linear functions that prevent the disclosure of any key information through the analysis of plaintext and ciphertext. These functions, in addition to uniformly distributing the input across the output space, increase the complexity of the encryption and its resistance to attacks such as **linear** and **differential cryptanalysis** due to their non-linearity. The **substitution box** is one of these confusion elements that maps **n** bits of input to **m** bits of output. S-boxes are typically static lookup tables used to provide non-linearity and create a complex Boolean relationship between the plaintext and ciphertext. S-box are suitable for software implementation because they can be stored in small memory. It should be noted that security can only be achieved by applying confusion properties. A **single-key lookup table** with 64-bit input and 64-bit output is strong enough, but because implementing this large lookup table is costly, most elements that apply confusion are combined with elements that apply diffusion so that confusion elements can be implemented with smaller lookup tables.

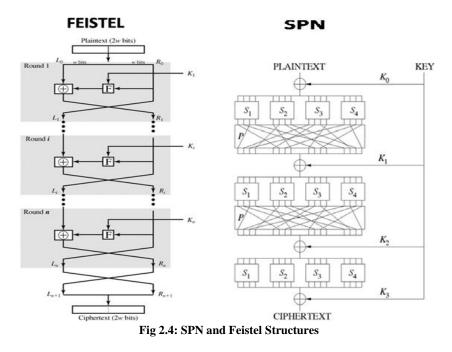

In the overall algorithm structure, there are different arrangements for confusion and diffusion functions. Two common structures, **SPN** (**Substitution-Permutation Network**) and **Feistel**, are illustrated in Figure 2.4 [12].

In the SPN (Substitution-Permutation Network) structure, the encryption operation is based on two actions: substitution and permutation. The combination of these two operations in a chained fashion adds sufficient complexity to the algorithm. In the Feistel structure, the input block is split into two halves: the left and the right. In each round, one half remains unchanged, while the other half undergoes a highly non-linear transformation through a function. Afterward, the two halves are swapped, and this process is repeated for multiple rounds. The strength of the encryption algorithm in the Feistel structure lies in the properties of this non-linear function. The key feature of the Feistel structure is that the encryption and decryption algorithms are identical, eliminating the need to invert the round function [15].

# 2.4.2 Stream Ciphers

A stream cipher, unlike block ciphers, operates by encrypting one bit at a time as it is received. The initial idea behind this encryption method is derived from the One-Time Pad (OTP). OTP is an encryption algorithm in which the plaintext is encrypted using a random key sequence equal to or longer than the message length. It has been proven that this encryption method is theoretically unbreakable, provided that the following four conditions are met [16]:

- 1. The length of the key used for encryption must be at least equal to or longer than the message being encrypted.

- 2. The key must be truly random, not generated by a simple computational function.

- 3. The key must be used only once; after its use, it should be immediately destroyed, both by the sender and the receiver.

- 4. There should only be two copies of the key: one for the sender and one for the receiver.

The advantage of this algorithm is its high speed in hardware, and its implementation is relatively simple. However, the primary challenge lies in the key size, which must always be at least as long as the plaintext. This raises issues related to key management and storage [14]. Figure 2.5 provides a representation of the structure of these algorithms [17].

Fig 2.5: Overall Structure for Stream Ciphers

Each stream cipher requires three stages for operation:

1. **Initialization Phase**: In this phase, the key and the initialization vector (IV) are loaded into the algorithm's states. The states are updated with several clock pulses, and this update process occurs without producing any output. The goal of this update is to combine the key with the IV in such a way that a change in the IV leads to a change in the pseudo-random bit sequence produced by the generator. After the initialization and preparation of the internal states, the

algorithm is ready for the next phase, which is the generation of the pseudorandom bit sequence.

- Encryption/Decryption Phase: In this phase, the pseudo-random bit sequence is generated by continuously updating the internal states of the algorithm, and this sequence is used for encryption or decryption by XORing it with the message or ciphertext.

- 3. **New Session Start**: After several exchanges between the sender and receiver, a new session is initiated with the release of a new initialization vector, although the initial key remains unchanged.

The core of a stream cipher is the pseudo-random bit sequence generator. The most important requirement for this part is that the generated sequence should depend more on the key and less on the initialization vector. To construct a pseudo-random bit sequence generator, suitable structures and mathematical operations, such as Linear Feedback Shift Registers (LFSR) and non-linear feedback mechanisms, can be used. These structures are well-suited for hardware implementation and have good statistical properties.

#### 2.4.3 Comparison

Each encryption method, whether block cipher or stream cipher, has its own set of advantages and disadvantages, which can be applied depending on their use case and environment. Table 2.2 summarizes these pros and cons.

| Feature                      | Stream Cipher         Block Cipher                             |                                  |

|------------------------------|----------------------------------------------------------------|----------------------------------|

|                              | -                                                              | -                                |

|                              |                                                                |                                  |

| Message Length               | Variable                                                       | Constant                         |

| memory                       | The algorithm has internal memory.                             | Cryptography is an in-place      |

|                              | Encryption does not depend only on                             | operation, and the result is not |

|                              | the message and key, but also on                               | stored anywhere. The output      |

|                              | previous changes made to the encoder,                          | does not depend on previous      |

|                              | which are stored in memory and affect                          | states or data.                  |

| Design Model                 | the new output.<br>Finite State Machine                        | Confusion+Diffusion              |

| Mathematical equvalence      | Psudeorandom Generator                                         | Psudeorandom Permutation         |

| Speed                        | In hardware applications: mostly fast                          | In hardware applications: low    |

| Specu                        | In software applications: faster                               | speed                            |

|                              | in software apprearons. Taster                                 | speed                            |

|                              |                                                                |                                  |

|                              |                                                                |                                  |

| Core                         | Encryption=Decryption                                          | Encryption+Decryption            |

|                              |                                                                |                                  |

| Implementation Complexity    | In hardware: They have low                                     | In hardware: They have high      |

|                              | implementation complexity.                                     | implementation complexity.       |

|                              | In software:                                                   |                                  |

|                              | Their correct implementation is difficult in both hardware and |                                  |

|                              | software, and they are vulnerable to                           |                                  |

|                              | weaknesses based on the application.                           |                                  |

|                              | Improper implementation causes                                 |                                  |

|                              | severe weaknesses in the application.                          |                                  |

| Buffering                    | No need for buffering                                          | Need for buffering               |

| Noise and Error Propagation  | Propagate noise                                                | They do not propagate errors.    |

|                              |                                                                | They are suitable for noisy      |

|                              |                                                                | channels.                        |

| Supporting Security Services | Confidentiality Yes                                            | Confidentiality Yes              |

|                              | Authentication No                                              | Authentication Yes               |

|                              | Integrity No                                                   | Integrity Yes                    |

| C. d                         | Non-repudiation No                                             | Non-repudiation No               |

| Cost                         | Low cost                                                       | Costy                            |

|                              | Most algorithms are designed for a                             |                                  |

| Application                  | specific application.<br>Secure Wireless Communications        | They become important where      |

| Application                  | Resource-Limited Devices                                       | communication security is        |

|                              | Resource-Linnica Devices                                       | critical.                        |

|                              |                                                                | viitivul.                        |

Table 2.2: Comparison of Features Between Block and Stream Ciphers

From this table, it can be inferred that block ciphers tend to be slower and have high hardware implementation costs, but they are less vulnerable to environmental factors such as noise and connection interruptions. On the other hand, stream ciphers, although faster and cheaper in terms of implementation, do not support data integrity, making them more vulnerable to incorrect implementations and security attacks.

Stream ciphers are more suitable for applications where speed is important, such as in real-time communications or on devices with limited computational resources, while block ciphers are more appropriate in environments requiring high security, especially where data integrity and authentication are critical.

#### 2.5 Existing Lightweight Symmentric Encryption Algorithms

Reviewing previous designs of lightweight symmetric encryption algorithms helps to identify the strengths and weaknesses of each algorithm. It is essential to remember that each encryption algorithm is designed with specific intentions and for a particular use case. The following examines the AEAD (Authenticated Encryption with Associated Data) algorithm and several lightweight cipher algorithms along with their features.

#### 2.5.1 Present Cipher

The key features of the PRESENT cipher, as cited from various sources, are as follows:

- It is a very lightweight block cipher designed by Axel Yorke-Pashman in 2007 and was chosen as a lightweight encryption standard in 2012.

- The block size is 64 bits, and the key sizes are either 80 or 128 bits.

- The algorithm uses the SPN (Substitution-Permutation Network) structure with 31 rounds.

- It was designed with a focus on hardware implementation.

- Security analysis indicates that attacks on the algorithm structure are effective up to a maximum of 26 rounds, and no effective attacks have been reported on its key generation function.

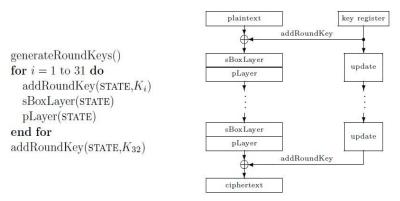

- Top Level Algorithm Descripton of algorithm is shown in Figure 2.6.

Fig 2.6: Top Level Algorithm Descripton of Present Cipher

#### 2.5.2 Boron Cipher

The key features of the Boron cipher, as cited by various sources, are as follows:

• It is a block cipher introduced in 2017 by Abahitaj at the University of Pune, India.

• The design of the Bouron cipher is based on the design principles of the PRESENT cipher, and its round structure and key generator are similar to those of the PRESENT algorithm.

- Security analysis of this algorithm has been conducted by the author himself.

- Top Level Algorithm Descripton of the algorithm is shown in Figure 2.7.

Fig 2.7: Top Level Algorithm Descripton of Boron Cipher

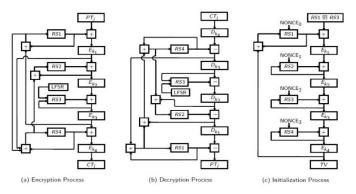

### 2.5.3 Hummingbrid Cipher

The key features of the Hummingburd cipher, as cited from various sources [18][19][20], are as follows:

• It is the only ultra-lightweight combined cipher designed by Zhen Zhen Fan in 2010.

• The cipher has a key length of 256 bits and 80-bit internal states. Upon analysis, the algorithm was found to be vulnerable to cryptanalysis. Additionally, the small size of its internal states makes it more vulnerable to stream cipher attacks.

• The improved version of this algorithm, called Hummingburd 2, has a block size of 16 bits, a key length of 128 bits, and a 128-bit state set, which is initialized by a 64-bit initialization vector (IV).

• The design logic of this algorithm is based on the Enigma machine. The encryption process can be viewed similarly to a rotating machine, where the block cipher components perform substitution on the 16-bit word.

• The Hummingburd2 algorithm is proprietary.

• Top Level Algorithm Descripton of the algorithm's structure is shown in Figure 2.8.

Fig 2.8: Top Level Algorithm Descripton of Hummingbird Encryption and Decryption

# 2.5.4 Comparison

The comparison of the previously designed ciphers—Present, Boron, and Hummingbird—is shown in Table 2.3:

| <u>Cipher</u> | Block Size | Key Length | Structure    | Year |

|---------------|------------|------------|--------------|------|

| Present       | 64         | 128-bit    | Block        | 2007 |

| Boron         | 64         | 128-bit    | Block        | 2018 |

| Humingbird    | 16         | 256-bit    | Stream-Block | 2014 |

Table 2.3: Comparison of Several Common Lightweight Ciphers

# **Summary and Conclusion**

In this chapter, we reviewed various cryptographic systems, compared their structures, and examined different fundamental encryption methods, including their advantages and disadvantages. This provided us with a general overview of these systems. Studying each cipher algorithm and understanding its key features and applications will help us in designing our own new algorithm. In the next chapter, we will apply the principles and features gained from the reviewed algorithms to propose a new algorithm based on the results obtained.

# Chapter 3: Design and Implementation of the Proposed Algorithm

# **Chapter Objectives:**

- 1. Conceptualization of the SEPAR Algorithm Design

- 2. Implementation of the SEPAR Algorithm

- 3. Evaluation of the Implementation Results

# Introduction

In this chapter, we present a newly designed lightweight algorithm named "SEPAR." The primary objective of its design is its application in devices used on the Internet of Things (IoT) environment, including ultra-lightweight devices.

#### **3.1 Design Strategy**

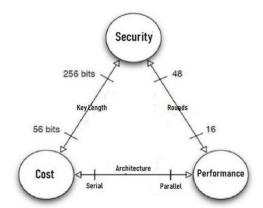

The main challenge in designing a lightweight cipher is achieving a balance between three parameters: security, cost, and performance. The ideal goal in the design of lightweight algorithms is to create and generalize innovative and novel algorithms that are implemented in a small space, with high speed, low power consumption, and, at the same time, security. Figure 3.1 illustrates the perspective of achieving balance in the design of a lightweight cryptographic algorithm [21].

Fig 3.1: Design Trade-offs for lightweight cryptographic algorithms[23]

In the design of a lightweight cryptographic algorithm, we must always maintain a balance between the three parameters mentioned in order to provide an optimized design. An example of the thought process for achieving this balance can be stated as follows: as the key size increases, the provided security increases, but this leads to a decrease in performance due to the rise in key processing rounds, resulting in higher costs in the design.

It should be noted that lightweight cryptographic algorithms use mathematical operators that have a low computational burden. The use of finite field computations in the design of lightweight algorithms is not necessarily due to the high computational power required. Additionally, four-bit S-box should always be used instead of eight-bit boxes to optimize memory usage.

# **3.2 SEPAR Cryptographic System**

SEPAR cipher is designed by combining block ciphers and stream ciphers. Its input length is 16 bits, key length is 256 bits, and its internal memory length is 144 bits. The appropriate choice of key length and internal state size not only suits most resource-constrained devices but also provides sufficient security. Table 3.1 contains the common notations used in this cryptographic system.

|            | Table 5.1. Notations used in the description of 5121 MK cipiter                           |

|------------|-------------------------------------------------------------------------------------------|

| KEY        | the 256-bit master key                                                                    |

| Ki         | the 32-bit segment key which drives by dividing the master key to 8 equal segments and    |

|            | used in <i>Enc_block</i> <sub>i</sub> , i = 1,2, ,8                                       |

| <u>k</u> i | the 16-bit subkey used in each Enc_block, i =1,2, ,6                                      |

|            |                                                                                           |

| State_i    | the i-th state which i is number , i = 1,2, ,9                                            |

| PT         | the 16-bit plaintext                                                                      |

| СТ         | the 16-bit ciphertext                                                                     |

| XOR        | Exclusive-or (XOR) operator                                                               |

| ()<br>n    | Right circular shift operator, which rotates all bits of its input to the right by n bits |

| (in )      | Left circular shift operator, which rotates all bits of its input to the left by n bits   |

|            | module 2 <sup>16</sup> addition operator                                                  |

|            | module 2 <sup>16</sup> subtraction operator                                               |

Table 3.1: Notations used in the description of SEPAR cipher

#### **3.2.1 Initialization Process**

Fig 3.2: SEPAR initialization algorithm

The Overall structure of the initialization algorithm can be seen in Figure 3.2. Before starting the encryption process, the initialization algorithm is executed. During the execution of the initialization algorithm, eight random 16-bit values are placed into the eight internal states of the initialization algorithm and are processed for four consecutive rounds. At the end of the execution, the eight current states of the initialization algorithm are copied into the eight internal states of the encryption algorithm. Additionally, the final value generated at the end of the fourth round, after modifying its 7th bit to 1, is stored in state number 9 of the encryption algorithm. The pseudocode of the initialization algorithm process is shown in Pseudocode (3.1).

Input: Eight 16-bit random integers known as a nonce **Output**: Initialized eight states State i (i=1,2, 3,...,8) and LFSR 1: state<sub>1</sub> = NONCE<sub>1</sub>  $2: state_2 = NONCE_2$ 3: state<sub>3</sub> = NONCE<sub>3</sub> 4: state<sub>4</sub> = NONCE<sub>4</sub>  $5: state_5 = NONCE_5$  $6: state_6 = NONCE_6$  $7: state_7 = NONCE_7$ 8: state<sub>8</sub> = NONCE<sub>8</sub> 9: **for** t = 0 to 3 **do** 10:  $V12_t = Enc_Block_{k_1}(((state1_t \boxplus state3_t) \boxplus state5_t) \boxplus state7_t)$ 11:  $V23_t = Enc_Block_{k_2}(V12_t \boxplus state2_t)$ 12:  $V34_t = Enc_Block_{k_3}(V23_t \boxplus state3_t)$ 13:  $V45_t = Enc_Block_{k_4}(V34_t \boxplus state4_t)$ 14:  $V56_t = Enc_Block_{k_5}(V45_t \boxplus state5_t)$ 15:  $V67_t = Enc_Block_{k_6}(V56_t \boxplus state6_t)$ 16:  $V78_t = Enc_Block_{k_7}(V67_t \boxplus state7_t)$ 17:  $Out_t = Enc_Block_{k_8}(V78_t \boxplus state8_t)$ 18:  $state1_{t+1} = state1_t \boxplus Out_t$ 19:  $state2_{t+1} = state2_t \boxplus V12_t$ 20:  $state3_{t+1} = state3_t \boxplus V23_t$ 21:  $state4_{t+1} = state4_t \boxplus V34_t$ 22:  $state5_{t+1} = state5_t \boxplus V45_t$ 23:  $state6_{t+1} = state6_t \boxplus V56_t$ 24:  $state7_{t+1} = state7_t \boxplus V67_t$ 25:  $state8_{t+1} = state8_t \boxplus V78_t$ 26: end for  $27: LFSR = Out_3 | 0x100$ 28: **return** statei<sub>7</sub> (i = 1, ..., 8) and LFSR

Algorithm 2: SEPAR Initialization Algorithm

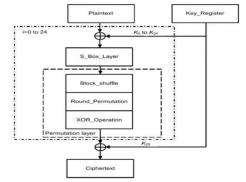

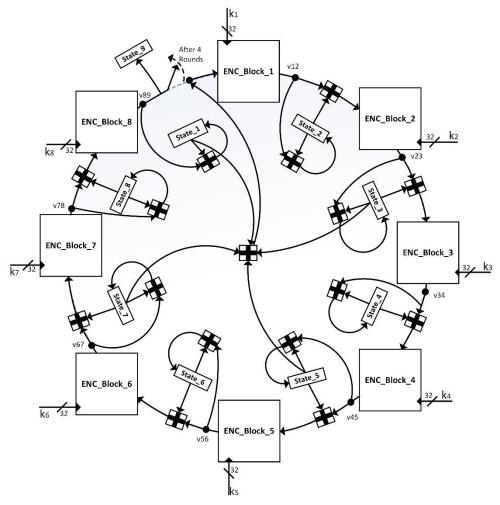

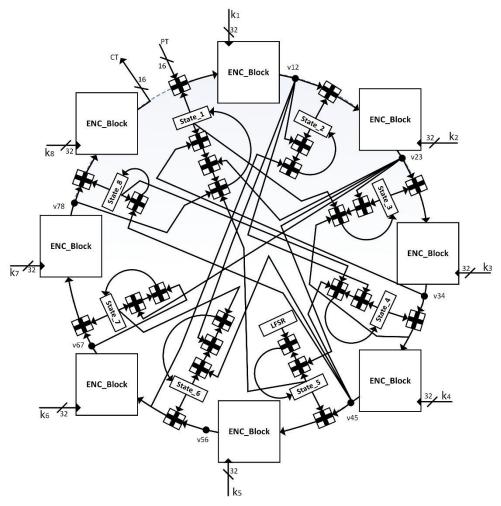

# 3.2.2 Encryption Process

Fig 3.3: SEPAR Encryption Process

The overall structure of the encryption algorithm is shown in Figure 3.3. After completing the preparation process, the encryption process is carried out by this algorithm. Pseudocode (3.2) clarifies the workflow of this algorithm.

```

Pseudocode (3.2): SEPAR encryption algorithm

Input: A 16-bit plaintext (PT), eight 16-bit states (State_i) and LFSR

Output: A 16-bit ciphertext (CT)

1: V12_t = Enc_Block_{k_1}(PT \boxplus state1_t)

2: V23_t = Enc\_Block_{k_2}(V12_t \boxplus state2_t)

3: V34_t = Enc_Block_{k_3}(V23_t \boxplus state3_t)

4: V45_t = Enc_Block_{k_4}(V34_t \boxplus state4_t)

5: V56_t = Enc_Block_{k_5}(V45_t \boxplus state5_t)

6: V67_t = Enc_Block_{k_6}(V56_t \boxplus state6_t)

7: V78_t = \text{Enc}_{Block}_{k_7}(V67_t \boxplus \text{state}_{7_t})

8: CT_i = Enc_Block_{k_8}(V78_t \boxplus state8_t)

9: LFSR_{t+1} \leftarrow LFSR_t

10: state2<sub>t+1</sub> = V12<sub>t</sub> \boxplus V56<sub>t</sub> \boxplus state6<sub>t</sub>

11: state3_{t+1} = V23_t \boxplus state_{t+1} \boxplus state_t

12: state4<sub>t+1</sub> = V12<sub>t</sub> \boxplus V45<sub>t</sub> \boxplus state8<sub>t</sub>

13: state5_{t+1} = V23_t \boxplus LFSR_{t+1}

14: state6_{t+1} = V12_t \boxplus V45_t \boxplus state7_t

15: \operatorname{state7}_{t+1} = \operatorname{V23}_t \boxplus \operatorname{V67}_t

16: \operatorname{state8}_{t+1} = \operatorname{V45}_t

17: \operatorname{state1}_{t+1} = \operatorname{V34}_t \boxplus \operatorname{V23}_t \boxplus \operatorname{V78}_t \boxplus \operatorname{state5}_t

18: return CT

```

29

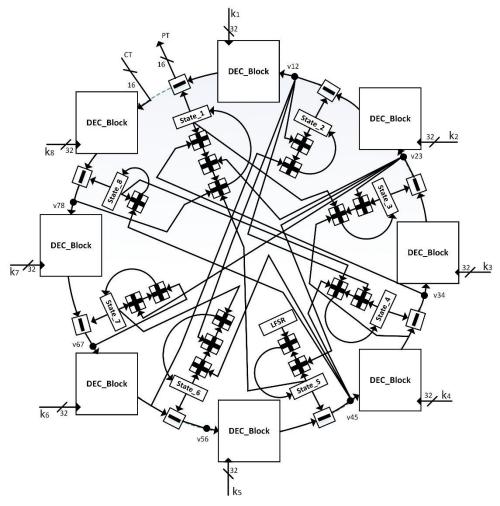

# 3.2.3 Decryption Process

Fig 3.4: SEPAR Decryption process

The overall structure of the decryption algorithm is shown in Figure 3.4. The decryption process follows the same pattern as the encryption process but is executed in reverse. The details of the algorithm are provided in pseudocode (3.3).

Pseudocode (3.3): SEPAR decryption algorithm Input: A 16-bit ciphertext (CT) and eight 16-bit states(State\_i) Output: A 16-bit plaintext(PT) 1: V78<sub>t</sub> = DEC\_Block<sub>k8</sub>(CT)  $\boxminus$  state8<sub>t</sub> 2: V67<sub>t</sub> = DEC\_Block<sub> $k_7$ </sub>(V78<sub>t</sub>)  $\boxminus$  state7<sub>t</sub>  $3: V56_t = DEC_Block_{k_6}(V67_t) \boxminus state6_t$ 4:  $V45_t = DEC_Block_{k_5}(V56_t) \boxminus$  state5<sub>t</sub>  $5: V34_t = DEC_Block_{k_4}(V45_t) \boxminus state4_t$ 6:  $V23_t = DEC_Block_{k_3}(V34_t) \boxminus$  state $3_t$  $7: V12_t = DEC_Block_{k_2}(V23_t) \boxminus state2_t$ 8:  $PT_i = DEC_Block_{k_1}(V12_t) \boxminus state1_t$ 9:  $LFSR_{t+1} \leftarrow LFSR_t$ 10: state $2_{t+1} = V12_t \boxplus V56_t \boxplus$  state $6_t$ 11: state $3_{t+1} = V23_t \boxplus state_{t+1} \boxplus state_t$ 12: state4<sub>t+1</sub> = V12<sub>t</sub>  $\boxplus$  V45<sub>t</sub>  $\boxplus$  state8<sub>t</sub> 13: state5<sub>t+1</sub> = V23<sub>t</sub>  $\boxplus$  LFSR<sub>t+1</sub> 14: state $6_{t+1} = V12_t \boxplus V45_t \boxplus state7_t$ 15: state7 $_{t+1} = V23_t \boxplus V67_t$ 16: state $8_{t+1} = V45_t$ 17: state $1_{t+1} = V34_t \boxplus V23_t \boxplus V78_t \boxplus$  state $5_t$ 18: return PT

#### 3.2.4 Key Generation Algorithm

SEPAR algorithm can be implemented without a fixed key generator, and the subkeys can be generated on the fly; However for enhanced security, a very lightweight key generator is proposed, which is designed with time and memory optimization in mind, while also ensuring resistance to key generation attacks. The pseudocode for generating subkeys is presented in pseudocode (3.4).

```

pseudocode (3.4): Key Generator Algorithm

```

```

Input: A 256-bit master key(KEY) and Number of Enc_block(n)

Output: Six 16-bit Subkeys(\underline{\mathbf{k}_{i}})

1: KEY = K<sub>1</sub> || K<sub>2</sub> || K<sub>3</sub> || K<sub>4</sub> || K<sub>5</sub> || K<sub>6</sub> || K<sub>7</sub> || K<sub>8</sub>

2: K<sub>j</sub> = k<sub>1</sub> || k<sub>2</sub> . j = 1.2.3.4.5.6.7.8

3: \underline{\mathbf{k}_1} = \mathbf{k}_1

4: \underline{\mathbf{k}_2} = \mathbf{k}_2

5: \underline{\mathbf{k}_3} = \text{SBOX}((\mathbf{k}_1 \iff 6)[7.8.9.10]) \oplus n + 2

6: \underline{\mathbf{k}_4} = \text{SBOX}((\mathbf{k}_2 \iff 10)[7.8.9.10]) \oplus n + 3

7: \underline{\mathbf{k}_5} = \mathbf{k}_1 \oplus \mathbf{k}_2

8: \underline{\mathbf{k}_6} = \underline{\mathbf{k}_3} \oplus \underline{\mathbf{k}_4}

9: return \underline{\mathbf{k}_i} . i = 1.2.3.4.5.6

```

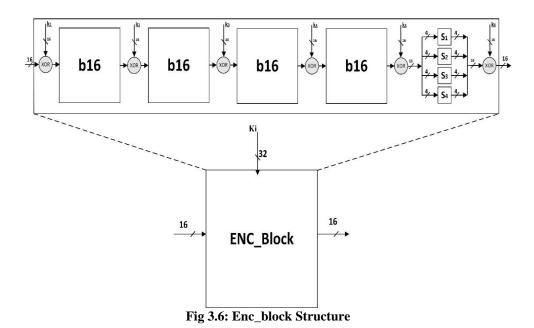

#### 3.2.5 16-bit Block Cipher

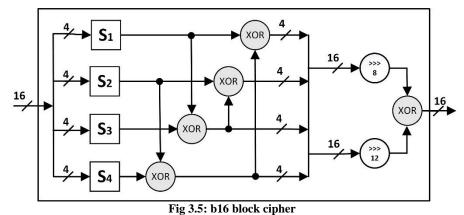

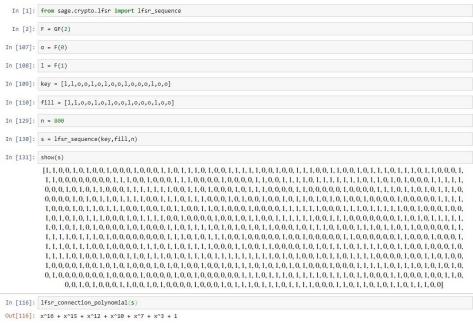

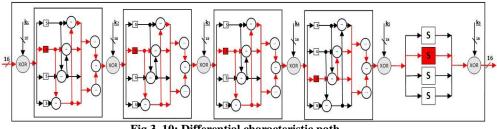

In the encryption process, SEPAR algorithm uses eight 16-bit blocks, referred to as **Enc-blocks**. Each **Enc-block** employs a block cipher function called **b16** in its structure. The internal structure of **b16** is an SP network, as shown in Figure 3.5. The substitution layer is implemented using four S-box (S-boxes).

Each Enc-block consists of a consecutive sequence of four b16 encoders and a substitution box layer. The hexadecimal representation of the four S-box used in b16 is provided in Table 3-2.

Table 3-2: Selected Four S-boxes in Hexadecimal Notation

| х        | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | Α | B | С | D | Ε | F |

|----------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| $S_1(x)$ | 1 | F | В | 2 | 0 | 3 | 5 | 8 | 6 | 9 | С | 7 | D | А | Е | 4 |

| $S_2(x)$ | 6 | А | F | 4 | Е | D | 9 | 2 | 1 | 7 | С | В | 0 | 3 | 5 | 8 |

| $S_3(x)$ | С | 2 | 6 | 1 | 0 | 3 | 5 | 8 | 7 | 9 | В | Е | А | D | F | 4 |

| $S_4(x)$ | D | В | 2 | 7 | 0 | 3 | 5 | 8 | 6 | С | F | 1 | А | 4 | 9 | Е |

The choice of the four S-box is based on the results obtained from the research [22], which, through extensive analysis of desirable 4-bit S-box, identified a set of S-box called "golden S-box." The security features present in these boxes ensure that encryption algorithms remain resilient to most significant attacks, particularly linear and differential attacks. In subsection 3-2-5-1, we further explore these criteria. The permutation layer used in **b16** is implemented with simple bitwise addition and rotation operators, providing adequate diffusion properties. The key mixing stage in this structure is straightforward, achieved with a bitwise addition operation. The four extracted 16-bit subkeys ( $k_1, k_2$ ,  $k_3, k_4$ ) from the 32-bit key section are bitwise added to each **b16**. Additionally, the

two 16-bit subkeys ( $k_5, k_6$ ) are bitwise added to their corresponding substitution layer within the **Enc-block**.

Figure 3.6 illustrates the overall structure of the **Enc-block** structure, and the pseudocode for the execution of the **Enc-block** operation is provided in pseudocode (3.5).

| Pseudocode (3.5): Er | c_block operation process |

|----------------------|---------------------------|

|----------------------|---------------------------|

Input: 16-bit input (m) and six 16-bit subkeys (ki) 1. 2. **Output**: A 16-bit data block (m<sup>'</sup>) 3. 1: **for** j = 1 to 4 **do** 4. 5. 2:  $m \leftarrow m \oplus \mathbf{k_i}$  $A = m_0 ||m_1||m_2||m_3$   $B = m_4 ||m_5||m_6||m_7$ 6. 3: 7.  $C = \mathbf{m}_8 ||\mathbf{m}_9||\mathbf{m}_{10}||\mathbf{m}_{11} \quad D = \mathbf{m}_{12} ||\mathbf{m}_{13}||\mathbf{m}_{14}||\mathbf{m}_{15}||\mathbf{m}_{14}||\mathbf{m}_{15}||\mathbf{m}_{14}||\mathbf{m}_{15}||\mathbf{m}_{14}||\mathbf{m}_{15}||\mathbf{m}_{14}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}_{15}||\mathbf{m}$ 8. 4: 9. 5:  $m \leftarrow A||B||C||D$ 10. 6:  $\mathbf{m} \leftarrow \mathbf{m} \oplus (\mathbf{m} \ll 8) \oplus (\mathbf{m} \ll 12)$ 11. 7: 12. 8: end for 13. 9: m  $\leftarrow$  m  $\oplus$  **k**<sub>5</sub> 14. 10:  $A = m_0 ||m_1||m_2||m_3$   $B = m_4 ||m_5||m_6||m_7$  $C = m_8 ||m_9||m_{10}||m_{11}$   $D = m_{12} ||m_{13}||m_{14}||m_{15}||m_{14}||m_{15}||m_{14}||m_{15}||m_{14}||m_{15}||m_{14}||m_{15}||m_{14}||m_{15}||m_{14}||m_{15}||m_{15}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}||m_{16}|$ 15. 16. 11:  $m \leftarrow S(A)||S(B)||S(C)||S(D)$ 17. 12: m'  $\leftarrow$  m  $\oplus$  <u>k</u><sub>6</sub> 18. 13: return m´ 19.

#### **3.2.5.1** Criteria for chosing S-Boxes

A 4-bit to 4-bit substitution box, is a Boolean vector function  $S(x) : \mathbb{F}_2^4 \rightarrow \mathbb{F}_2^4$ . Suppose  $x = (x_3 ||x_2||x_1||x_0)$  is a 4-bit input to the substitution box S(x). S-box can be represented in its boolean form as shown in (3-1):

$$S(x) = S^{(3)}(x)||S^{(2)}(x)||S^{(1)}(x)||S^{(0)}(x)$$

(3-1)